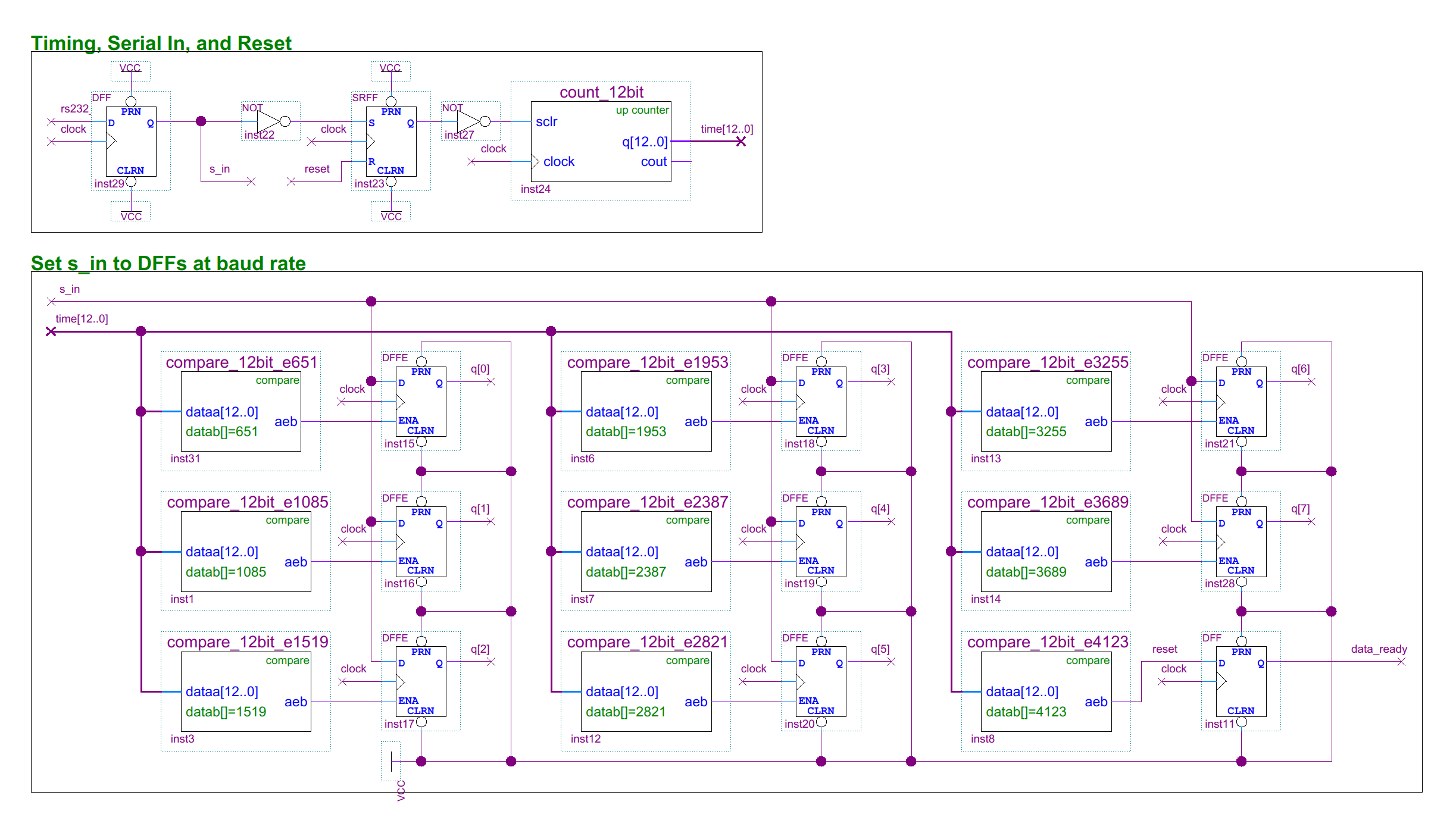

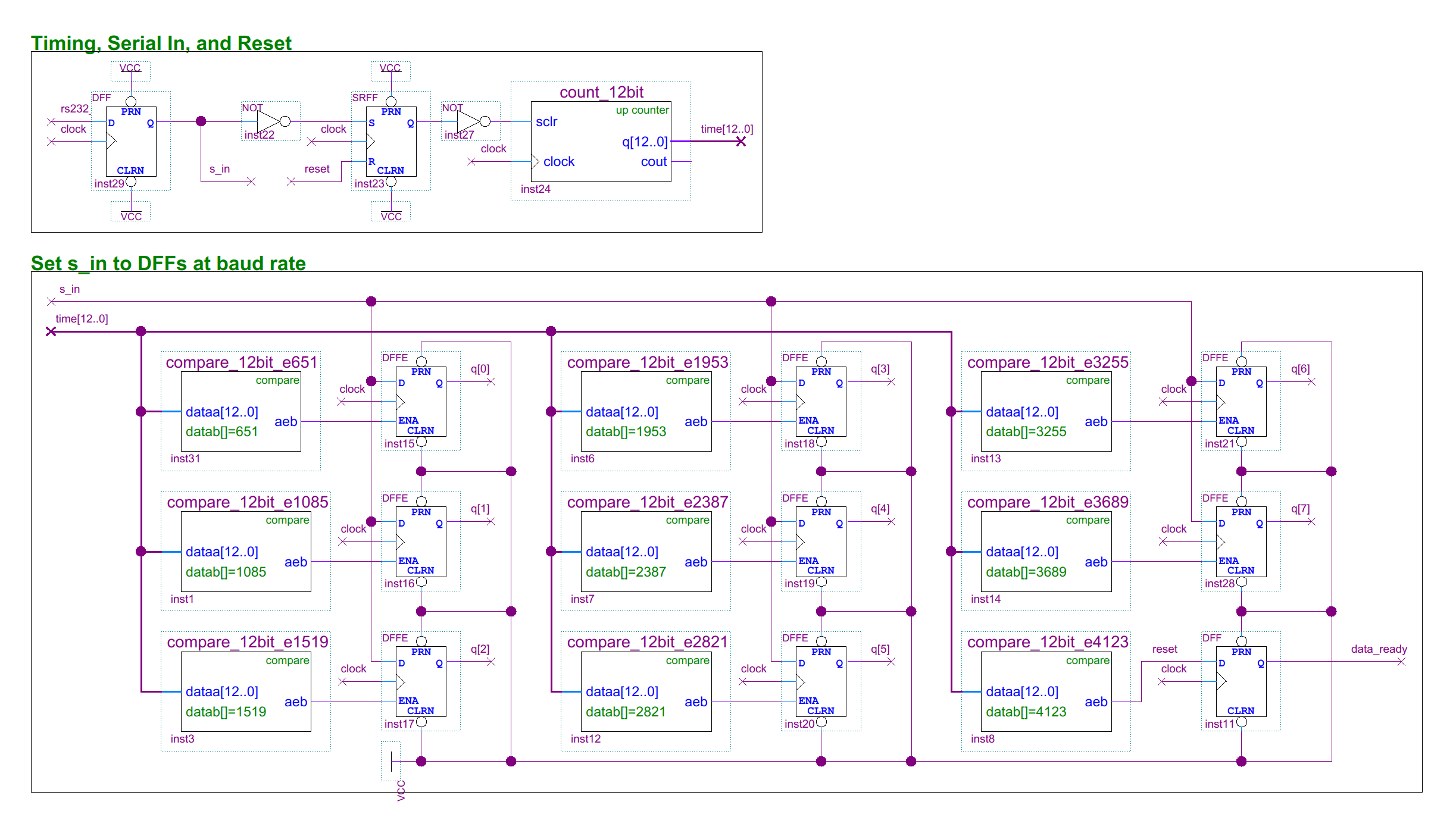

Here is how the RS-232 decoder works in Quartus. The "Timing, Serial In, and Reset" block takes the rs232_in signal and synchronizes it to the 50 MHz system clock. Then it sends the synchronized signal s_in to two places. The first is a set of 9 flip-flops described below, and the second is (through an inverter) to an SR flip-flop. The 12-bit counter in this block produces a number that counts up at 50 MHz. This counter is cleared by the "reset" line from the 9th flip-flop in the decoder (see below) when the decoder finishes decoding one byte, and it will then be made ready to clear again by the SR flip-flop the next time a new byte is received on the serial line. The s_in signal is fed to the D inputs of 8 separate D flip-flops, each of which will store one bit of the decoded byte from the serial line, for example q[0]. All 8 flip-flops are clocked at 50 MHz using the onboard system clock. The 8 decoder flip-flops have enable inputs that must be high for the s_in value to be sent to the q output. Each enable input is turned on for only one clock cycle by the corresponding magnitude comparator when the counter reaches a particular value (aeb: a=b). The values are the number of 50 MHz clock cycles that it takes to get to the center of the interval when the corresponding bit is coming in on the RS-232 line. For example (see the timing diagram here), the center of the start bit happens half way through the first interval, with each interval being 1/(baud rate) = 1/115200 = 8.68 us (us = microseconds). So this time would be (8.68 us)/2 = 4.34 us. The center of the q[0] data bit would be one interval later, which would be 8.68 + 4.34 = 13.02 us. 13.02 us is 651 50 MHz clock cycles (each of which is 20 ns), so the q[0] magnitude comparator is set to transfer the value of the q[0] bit from the s_in line when the counter value hits 651. Likewise, the center of the q[3] bit happens 4.5 intervals after the rising edge of the start bit, so the counter value at that time is 4.5*0.00000868*50000000 = 1953. Finally, the 9th magnitude comparator in the decoder sets the reset line for the counter high after 9.5 intervals, in the middle of the stop bit. 9.5*0.00000868*50000000 = 4123. The 9th flip-flop turns on the data_ready line at the next clock cycle rising edge.